10Project Based on Verilog HDLs

This chapter includes VLSI projects based on digital circuit design using Verilog programming and functional verification with a truth table on Xilinx tool [1–2]. The project includes all four levels of abstraction of Verilog from the switch-level to behavioral-level model. Each project gives a basic description of design including truth table and design verification results.

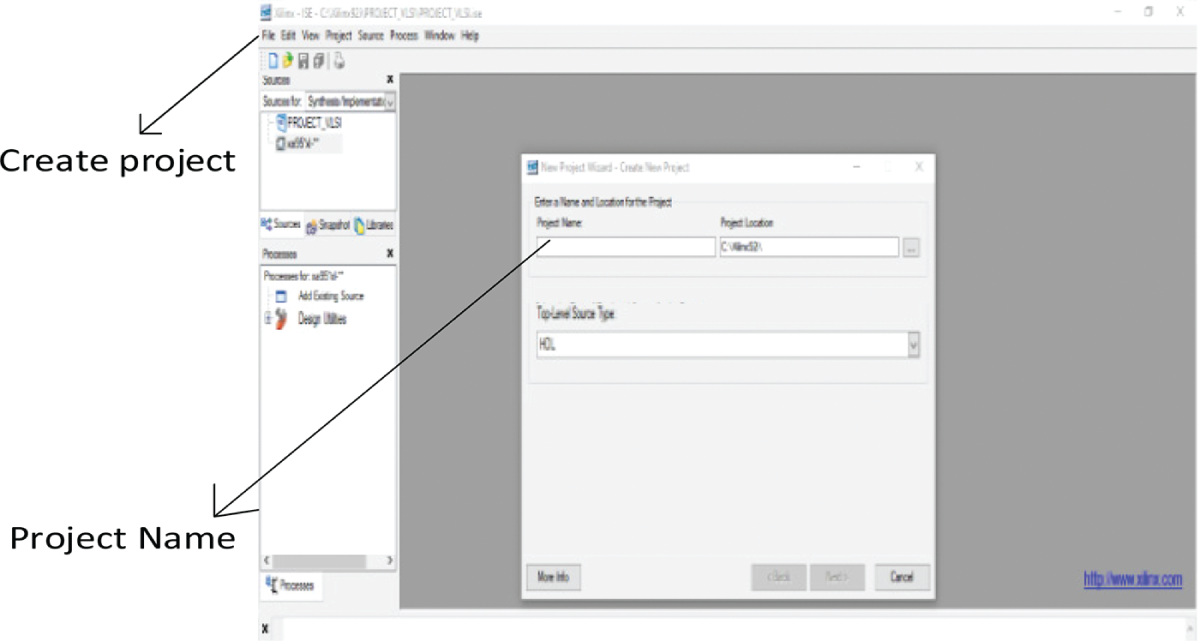

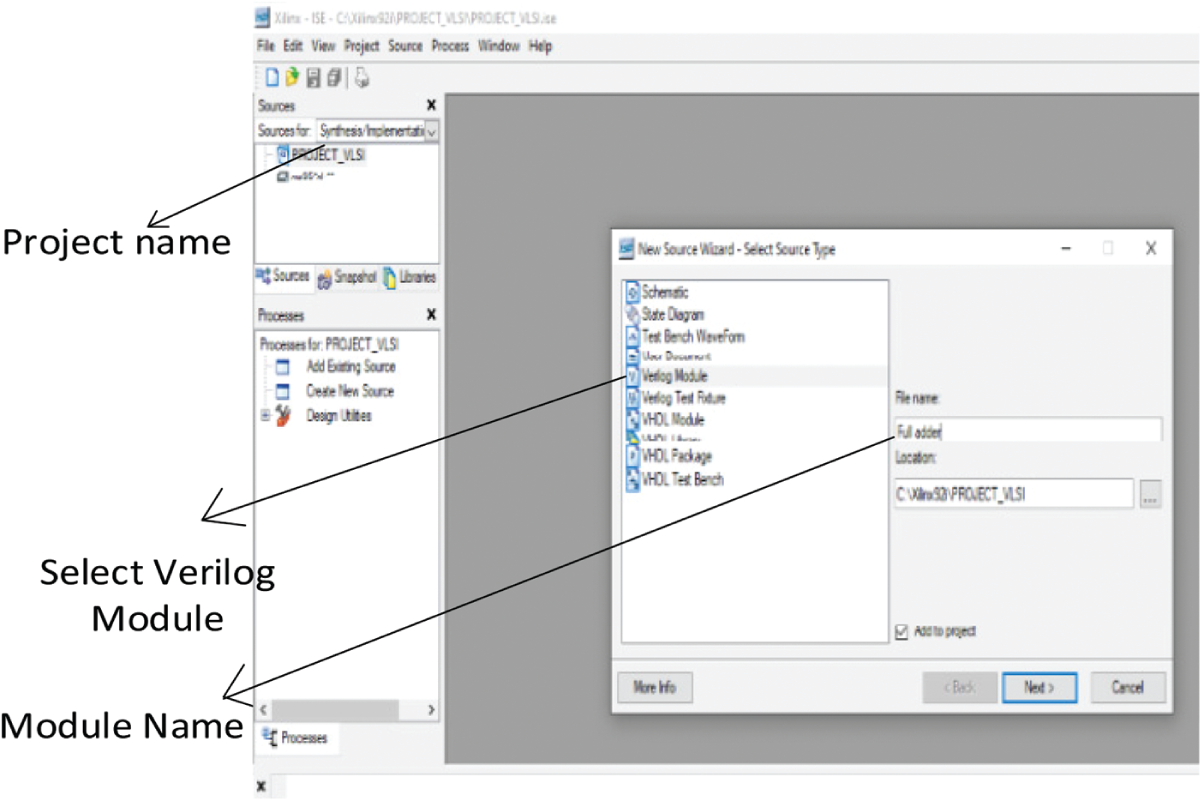

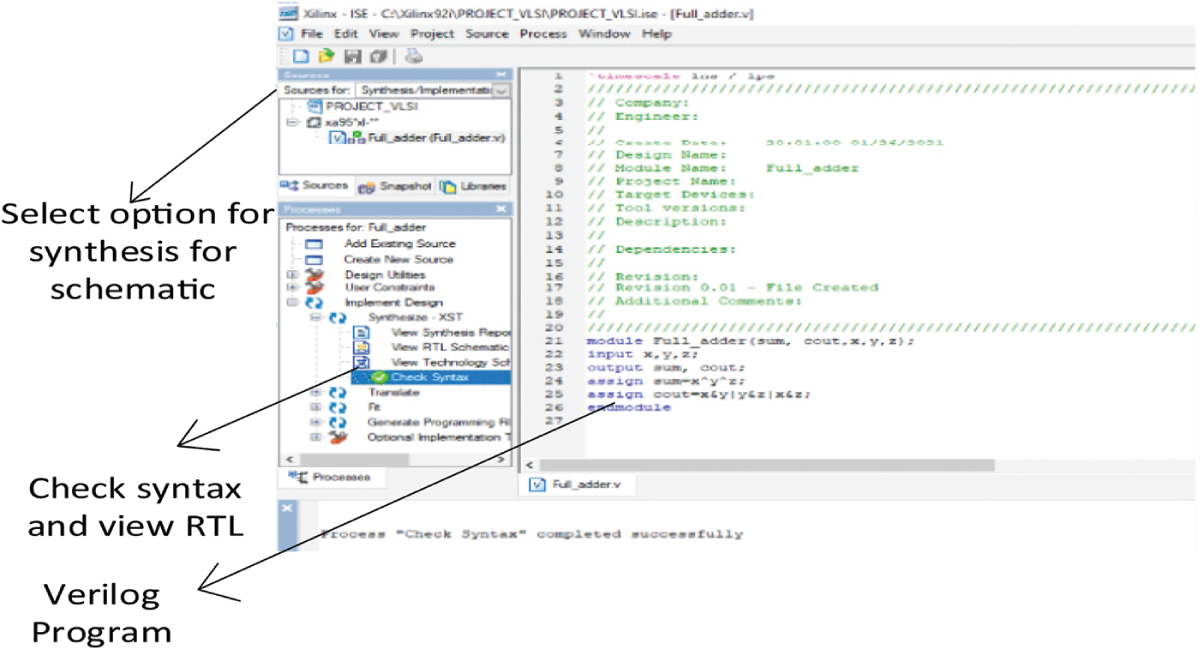

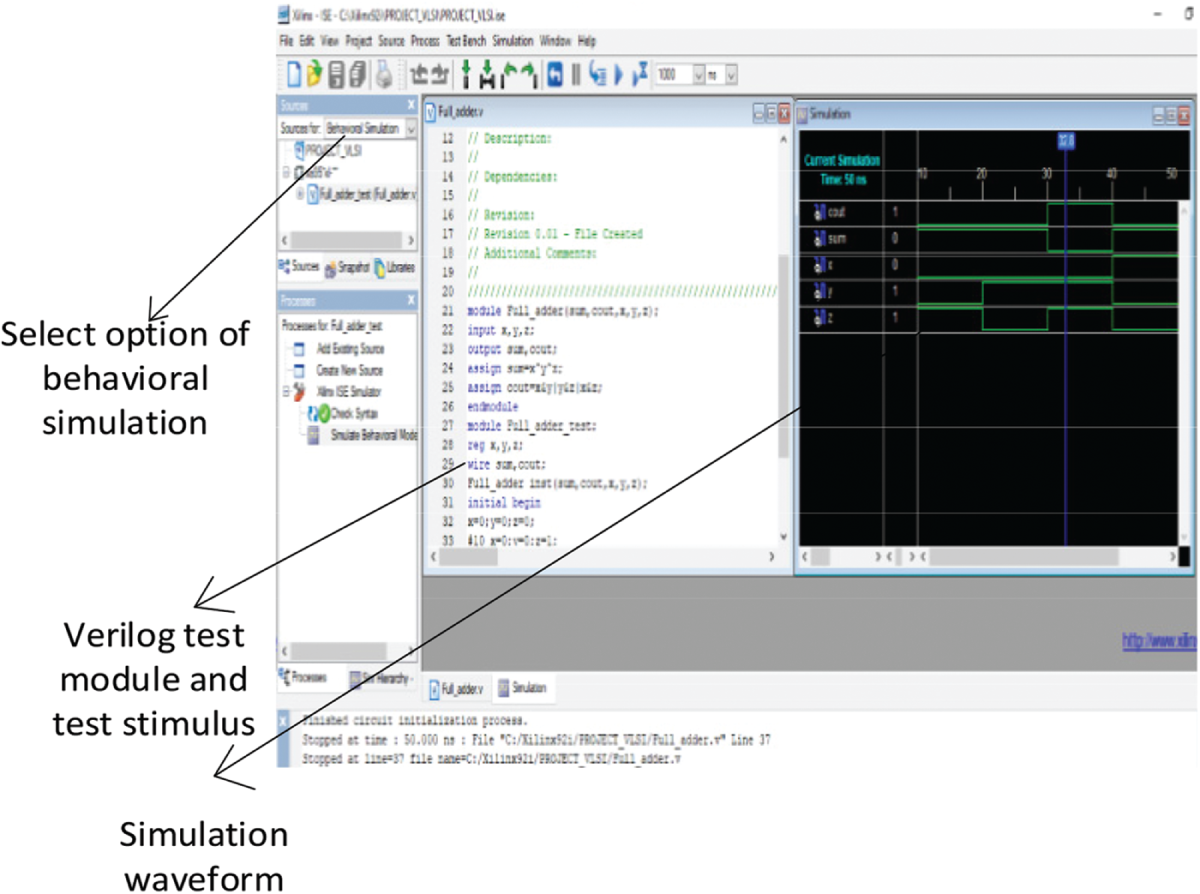

Xilinx ISE is one of the useful simulators that uses Verilog/VHDL languages to design and implement any digital logic virtually. Figures 10.1–10.4 show how the Xilinx ISE simulator interfaces to create a project, select the Verilog module, text editor, and waveform window, respectively.

Figure 10.1 New project creation on Xilinx ISE simulator.

Figure 10.2 New source module creation on Xilinx.

Figure 10.3 Xilinx platform for Verilog HDL.

Figure 10.4 Behavioral simulation on Xilinx platform.

Step 1: file → new project → project name

Step 2: Right click on project created → new source → select Verilog module → module name. Choose option next and finish.

Step 3: Write a Verilog program ...

Get Digital VLSI Design and Simulation with Verilog now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.