9 Programmable and Reconfigurable Devices

9.1 Logic Synthesis

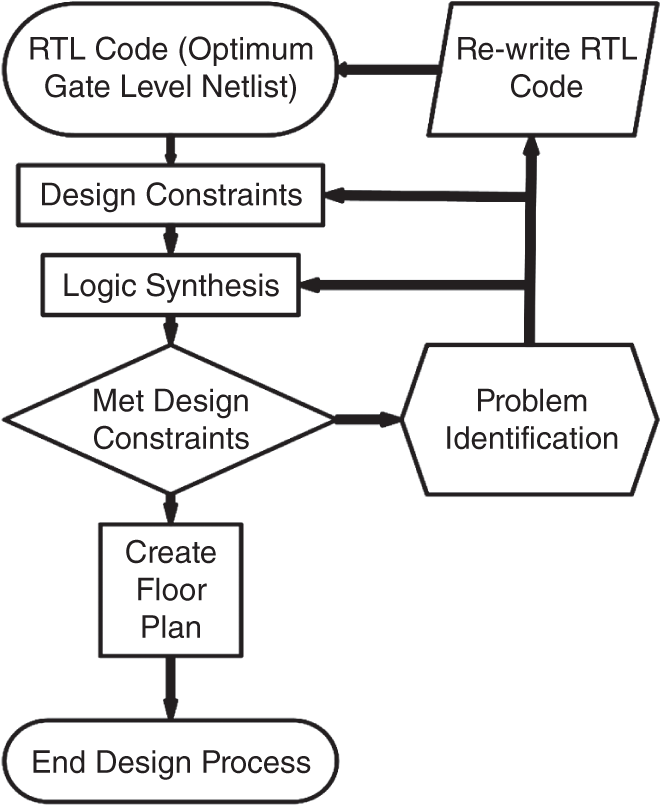

The design of a complex function is mainly performed through a higher level of abstraction such as behavioral or dataflow models. In logic synthesis, the designer works on getting the transistor level net list from the register transfer level (RTL) or a higher level of modules. The advantage of these higher levels is that a designer can easily solve and implement any digital circuit at algorithm or truth table with the knowledge of certain design specifications. The process of logic synthesis helps in achieving an optimum gate level netlist or logic implementation through higher-level Verilog models without any concern for internal connections, wires, and the number of components in comparison to the lower-level modules of gate-level or switch-level models. Logic synthesis plays an important role in complex digital circuit design in obtaining optimum hardware elements and interconnects. There are several ways to implement a particular digital function within the specified design constraints. So, getting an optimum design is a highly automated process that bridges the gap between high-level design synthesis and the physical-layout processes. Figure 9.1 shows a general workflow in logic synthesis. Logic synthesis includes standard cell libraries.

Figure 9.1 VLSI design flow at RTL level.

9.1.1 Technology Mapping ...

Get Digital VLSI Design and Simulation with Verilog now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.